## UG0733 User Guide Sinc3 Filter v4.2

Microsemi Corporate Headquarters One Enterprise, Aliso Viejo, CA 92656 USA

Within the USA: +1 (800) 713-4113 Outside the USA: +1 (949) 380-6100 Sales: +1 (949) 380-6136

Fax: +1 (949) 215-4996

E-mail: sales.support@microsemi.com www.microsemi.com

© 2018 Microsemi Corporation. All rights reserved. Microsemi and the Microsemi logo are trademarks of Microsemi Corporation. All other trademarks and service marks are the property of their respective owners.

Microsemi makes no warranty, representation, or guarantee regarding the information contained herein or the suitability of its products and services for any particular purpose, nor does Microsemi assume any liability whatsoever arising out of the application or use of any product or circuit. The products sold hereunder and any other products sold by Microsemi have been subject to limited testing and should not be used in conjunction with mission-critical equipment or applications. Any performance specifications are believed to be reliable but are not verified, and Buyer must conduct and complete all performance and other testing of the products, alone and together with, or installed in, any end-products. Buyer shall not rely on any data and performance specifications or parameters provided by Microsemi. It is the Buyer's responsibility to independently determine suitability of any products and to test and verify the same. The information provided by Microsemi hereunder is provided "as is, where is" and with all faults, and the entire risk associated with such information is entirely with the Buyer. Microsemi does not grant, explicitly or implicitly, to any party any patent rights, licenses, or any other IP rights, whether with regard to such information itself or anything described by such information. Information provided in this document is proprietary to Microsemi, and Microsemi reserves the right to make any changes to the information in this document or to any products and services at any time without notice.

#### **About Microsemi**

Microsemi Corporation (Nasdaq: MSCC) offers a comprehensive portfolio of semiconductor and system solutions for aerospace & defense, communications, data center and industrial markets. Products include high-performance and radiation-hardened analog mixed-signal integrated circuits, FPGAs, SoCs and ASICs; power management products; timing and synchronization devices and precise time solutions, setting the world's standard for time; voice processing devices; RF solutions; discrete components; enterprise storage and communication solutions, security technologies and scalable anti-tamper products; Ethernet solutions; Power-over-Ethernet ICs and midspans; as well as custom design capabilities and services. Microsemi is headquartered in Aliso Viejo, Calif., and has approximately 4,800 employees globally. Learn more at www.microsemi.com.

# **Contents**

| 1 | Revis  | ion History              |

|---|--------|--------------------------|

|   | 1.1    | Revision 2.1             |

|   | 1.2    | Revision 2.0             |

|   | 1.3    | Revision 1.0             |

| 2 | Introd | luction                  |

| 3 | Hard   | ware Implementation      |

|   | 3.1    | Timing Diagram           |

|   | 3.2    | Inputs and Outputs       |

|   | 3.3    | Configuration Parameters |

|   | 3.4    | Resource Utilization     |

# **Tables**

| Table 1 | Inputs and Outputs of Sinc3 Filter | 4 |

|---------|------------------------------------|---|

| Table 2 | Configuration Parameters           | 4 |

| Table 3 | Resource Utilization               |   |

# **Figures**

| Figure 1 | Block Diagram of Sinc3 Filter           | 3 |

|----------|-----------------------------------------|---|

| Figure 2 | Hardware Implementation of Sinc3 Filter | 3 |

| Figure 3 | Timing Diagram of Sinc3 Filter          | 4 |

### 1 Revision History

The revision history describes the changes that were implemented in the document. The changes are listed by revision, starting with the most current publication.

#### 1.1 Revision 2.1

The following is a list of changes done in revision 2.1 of this document.

- Figure 1, page 3 Block Diagram of Sinc3 Filter, is edited to replace the input signal hold\_i with reg\_rst\_i.

- Table 1, page 4 Inputs and Outputs of Sinc3 Filter, is edited to replace the input signal, hold\_i with reg\_rst\_i and its description.

#### **1.2** Revision 2.0

The following is a list of changes done in revision 2.0 of this document.

- Table 2, page 4 Configuration Parameters, is updated to add the configuration parameters g\_BIPOLAR and g\_NEGATE\_OUTPUT and their descriptions.

- A new equation to calculate the equivalent resolution of the Sinc3 filter output with respect to decimation factor is added in Hardware Implementation, page 3 below Figure 2, page 3.

- Figure 1, page 3 Block Diagram of Sinc3 Filter, is edited to add the input signal hold i.

- Table 1, page 4 Inputs and Outputs of Sinc3 Filter, is edited to add the input signal, hold\_i and its

description.

#### 1.3 **Revision 1.0**

Revision 1.0 (Published in September 2016) was the first publication of this document.

## 2 Introduction

Sinc3 filter is a low-pass filter, which removes all high frequency components above the cutoff frequency without affecting the frequencies below the cutoff frequency. An ideal Sinc3 filter requires an infinite delay. A practical Sinc3 filter has three stages of integration and three stages of differentiation at a decimated clock.

#### Sinc3 filter is used to:

- De-modulate data from a delta-sigma modulator, which is widely used in delta-sigma type analog-to-digital converter (ADC).

- · Convert the serial bitstream from ADC to parallel data.

## 3 Hardware Implementation

The following figure shows the block diagram of Sinc3 filter.

Figure 1 • Block Diagram of Sinc3 Filter

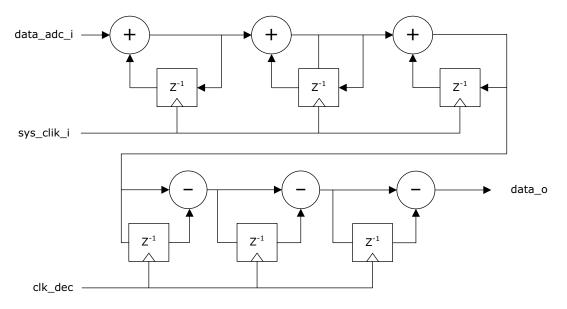

The following figure shows the hardware implementation of Sinc3 filter.

Figure 2 • Hardware Implementation of Sinc3 Filter

The clk\_adc\_i signal is the modulator clock from the ADC to the Sinc3 filter. The filter implements three sequential integrations at the rate of clk\_adc\_i. A decimated clock is generated internally based on configuration parameters as shown in the following equation. The output of the third integrator is differentiated serially three times with respect to decimated clock to generate the output.

$$f_{clk\_dec\_o} = f_{clk\_adc\_i} \times 2^{g\_DECIMATION\_FACTOR}$$

The equivalent resolution of the Sinc3 filter output with respect to decimation factor is represented by the following equation.

Equivalent Resolution (in bits) =  $(2 \times Decimation Factor)$

### 3.1 Timing Diagram

The following figure shows the timing diagram of Sinc3 filter.

Figure 3 • Timing Diagram of Sinc3 Filter

### 3.2 Inputs and Outputs

The following table lists the input and output ports of the Sinc3 filter.

Table 1 • Inputs and Outputs of Sinc3 Filter

| Signal Name | Direction | Description                                                                                                                                                                                      |

|-------------|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| reset_i     | Input     | Active low asynchronous reset signal to design.                                                                                                                                                  |

| clk_adc_i   | Input     | Modulator clock coming from ADC.                                                                                                                                                                 |

| data_adc_i  | Input     | Data bitstream from the modulator in ADC.                                                                                                                                                        |

| reg_rst_i   | Input     | When 1, resets all the registers. When 0, filter is normally operated.                                                                                                                           |

| clk_dec_o   | Output    | Decimated clock output. This is the same clock used for differentiator. The output of the filter updates at the rising edge of this output. This signal is not generated when res_rst_i is high. |

| data_o      | Output    | Filtered data output.                                                                                                                                                                            |

### 3.3 Configuration Parameters

The following table lists the configuration parameters used in the hardware implementation of the Sinc3 filter. These are generic parameters that vary according to the application requirements.

Table 2 • Configuration Parameters

| Name                | Description                                                                                                              |  |

|---------------------|--------------------------------------------------------------------------------------------------------------------------|--|

| g_STD_IO_WIDTH      | Width of the input and output signals.                                                                                   |  |

| g_DECIMATION_FACTOR | Division factor used to generate the decimated clock from the system clock input.                                        |  |

| g_BIPOLAR           | Select 0 if the ADC is unipolar,<br>Select 1 if ADC is bipolar.                                                          |  |

| g_NEGATE_OUTPUT     | Select 0 if the data at the data_o port should be negated. Select 1 if the data at data_o port should be passed through. |  |

#### 3.4 Resource Utilization

The following table lists the resource utilization of the Sinc3 filter IP implemented on SmartFusion2 $^{\text{@}}$  and IGLOO2 $^{\text{@}}$  devices with g\_STD\_IO\_WIDTH\_value equal to 18.

Table 3 • Resource Utilization

| Resource            | Usage |

|---------------------|-------|

| Sequential          | 220   |

| Combinational Logic | 160   |

| MACC                | 0     |

| RAM 1kx18           | 0     |

| RAM 64x18           | 0     |